|

12.3.2.5 explain three operations in fetch-execute cycle (fetch /decode /execute) Fetch-Decode-Execute cycle The processor responds to and processes the instructions that drive the computer. It contains the control unit, the arithmetic/logic unit (ALU) and registers. The control unit coordinates and controls all the operations carried out by the computer. It operates by repeating three operations:

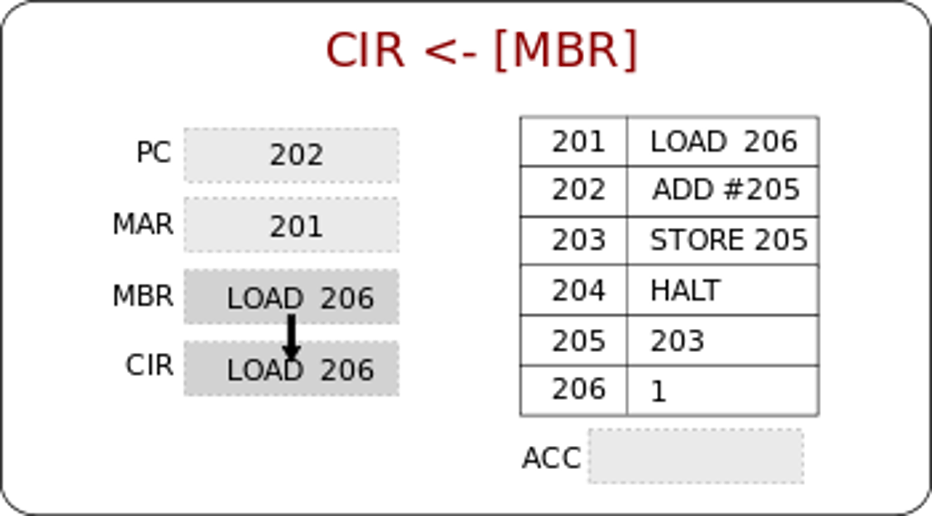

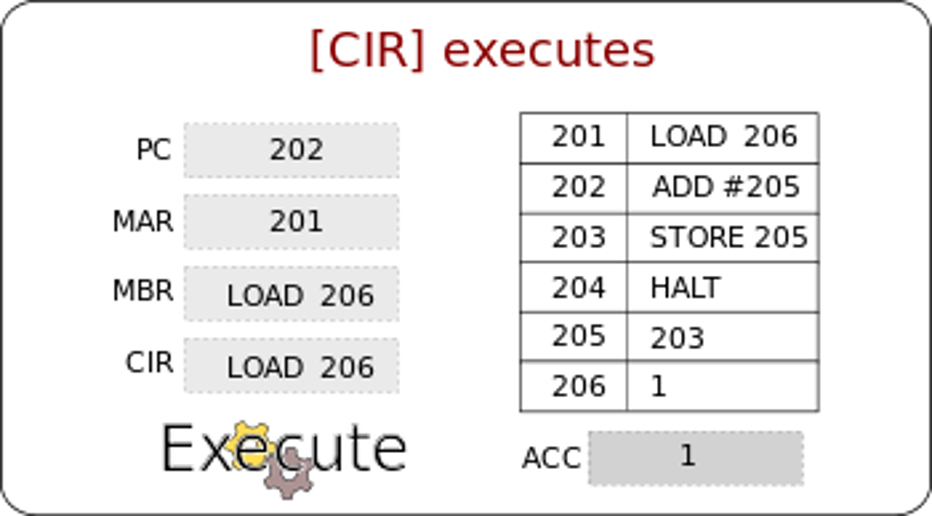

Decode - The decoding step is where the CPU understands/works out what the instruction it has just fetched actually means. Execute - The Execute stage is where data processing happens. Instructions are carried out on the data. When once a cycle has been completed, a new cycle begins. Watch video to 5:15 Author: Tom Scott Author: TeamComputing Registers/circuits involved The circuits used in the CPU during the cycle are:

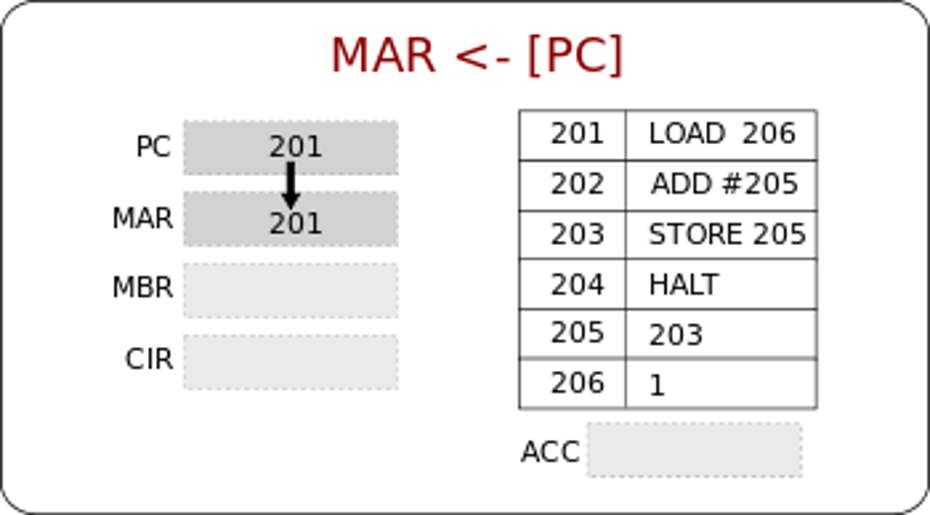

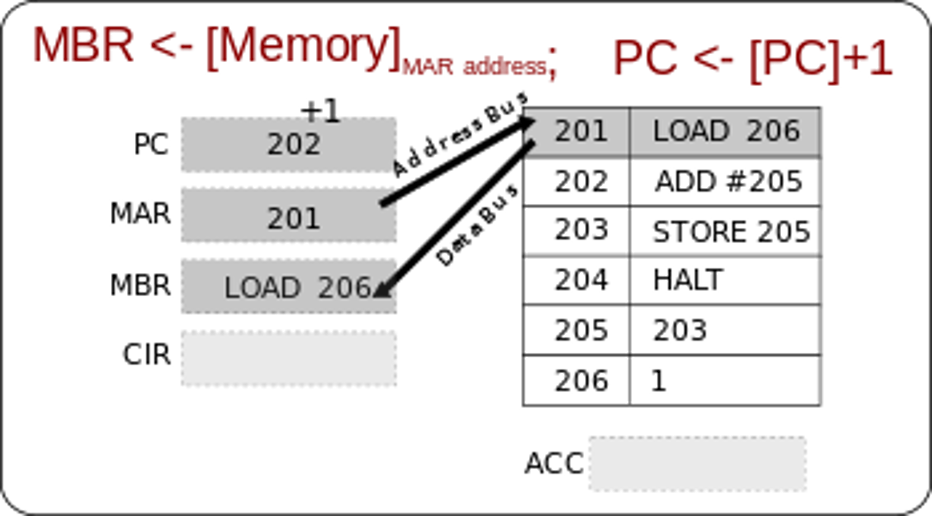

Control Unit (CU) - decodes the program instruction in the CIR, selecting machine resources such as a data source register and a particular arithmetic operation, and coordinates the activation of those resources. Arithmetic logic unit (ALU) - performs mathematical and logical operations. Register notation of the Fetch-Decode-Execute cycle Steps: MAR <== [PC]

MBR <== [Memory]MARaddress; PC <== [PC]+1  CIR <== [MBR]  [CIR] executes  Questions: Exercises: Ex. 1 Ex. 2 Ex. 3 Ex. 4 Ex. 5 Ex. 6 Exam questions:

| |

|

| |

| Просмотров: 12590 | | |

| Всего комментариев: 0 | |

Fetch - In this step, the CPU fetches some data and instructions from the main memory (RAM) and then store them in its own temporary memory called 'registers'

Fetch - In this step, the CPU fetches some data and instructions from the main memory (RAM) and then store them in its own temporary memory called 'registers'